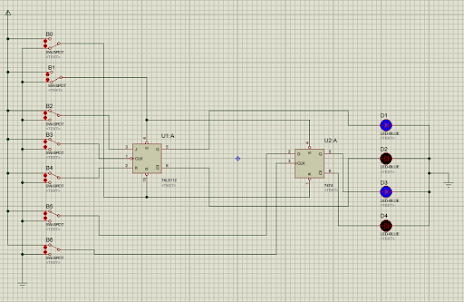

Pada kondisi pertama switch 1 berlogika 1 yaitu pada input S (Set) berlogika 1

pada J-K flip flop dan D flip flop maka pada output pada Q pada J-K flip flop

berlogika 0 dan kebalikannya pada Q' berlogika 1.

Pada D flip flop input S berlogika 1 maka output pada Q akan berlogika 0 dan pada Q' akan berlogika 1.

Kondisi ini sesuai dengan tabel kebenaran, dimana pada tabel kebenaran J-K flip flop ketika S diberi inputan 1 dan pin J dan K berlogika 0 dan clock low. Maka kondisi Q' nya tidak berubah yaitu berlogika 1 tetapi pada output Q berlogika 0.

Pada D Flip Flop sesuai dengan tabel kebenaran yang dimana jika input D dan Clock berlogika 0 maka output Q Reset ke 0 sehingga hanya Q' yang berlogika 1.

Pada kondisi kedua switch 0 berlogika 1 yaitu pada input R (Reset) berlogika

1 pada J-K flip flop dan D flip flop maka pada output pada Q pada J-K flip flop

berlogika 1 dan kebalikannya pada Q' berlogika 0.

Pada D flip flop input R berlogika 1 maka outputnya pada Q berlogika 1 dan pada Q' Berlogika 0.

Kondisi ini sesuai dengan tabel kebenaran, dimana pada tabel kebenaran J-K flip flop ketika R diberi inputan 1 dan pin J dan K berlogika 0 dan clock low maka kondisi Q' nya berubah menjadi berlogika 0.

Pada D Flip Flop didapatkan bahwa jika input D dan Clock

berlogika 0 yaitu Q berlogika 1 sehingga keadaanya tetap berlogika 1 yang

artinya dapat dilihat pada tabel kebenaran dengan keterangan bahwa

"menahan kondisi Q terakhir" dengan kata lain kondisinya tidak

berubah atau tetap. Yaitu pada

Q' ketika R diberi input 1 maka Q' akan berlogika 0.

Hasil analisa:

a.D flip-flop

b. JK flip-flop

Hasil Percobaan:

Dapat dilihat dari data hasil percobaan dan tabel kebenaran mempunyai kesesuaian sehingga dapat dikatakan bahwa hasil percobaan sama dengan tabel kebenaran dari jk-flipflop dan d-flipflop

Tidak ada komentar:

Posting Komentar