DAFTAR ISI

3. Download

1. JFET Common-Gate Configuration

1.1 Tujuan [Kembali]

- Untuk mengetahui tentang JFET common-gate configuration

- Bisa membuat rangkaian JFET common-gate confoguration

Fitur impedansi input yang tinggi dari koneksi sebelumnya hilang dalam konfigurasi ini karena gerbang umum memiliki impedansi masukan yang rendah, tetapi impedansi output yang tinggi.

Jenis konfigurasi FET digunakan dalam Sirkuit Frekuensi Tinggi atau Rangkaian Pencocokan Impedansi yang Impedansi Input yang Rendah harus dicocokkan dengan Impedansi Output yang Tinggi. Outputnya "In-Phase" dengan Input.

1.3 Gambar [Kembali]

1.4 Teori [Kembali]

Dengan mengganti rangkaian ekivalen JFET akan menghasikan gambar 9.30

Perhatikan syarat berkelanjutan bahwa sumber yang dikendalikan gmVgs dihubungkan dari drain menuju source dengan rd dalam posisi paralel. Isolasi antara rangkaian input dan output telah hilang ketika terminal gerbang terhubung ke common ground dari jaringan. Selain itu, resistor yang terhubung antara terminal input tidak lagi RG tetapi resistor RS yang terhubung dari sumber ke ground. Perhatikan juga lokasi tegangan pengontrol Vgs dan fakta bahwa tegangan itu muncul langsung di resistor RS.

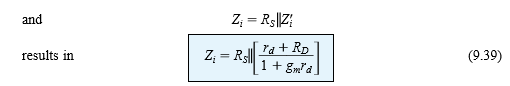

Zi: Resistor Rs langsung melewati terminal yang didefenisikan Zi. Tentukan impedansi Zi' dari gambar 9.29, di mana akan paralel dengan Rs jika Zi terdefenisi.

Rangkaian digambar ulang seperti gambar 9.31

Dengan mengaplikasikan KVL di sekitar parameter output maka dihasilkan

Dengan mengaplikasikan KCL pada node a didapatkan

Zo: Substitusikan Vi = 0V pada gambar 9.30 akan men-"short-out" efek dari Rs dan atur Vgs ke 0V. hasilnya adalah gmVgs akan sama dengan nol dan rd akan paralel dengan RD. Sehingga,

Av: Gambar 9.30 membuktikan bahwa,

Dengan mengaplikasikan KCL pada node b pada gambar 9.30 menghasilkan,

untuk rd ≥ 10RD,

Hubungan fase: fakta bahwa Av adalah bilangan positif akan menghasilkan hubungan in-phase antara Vo dan Vi untuk konfigurasi common-gate

2. Rangkaian Simulasi

2.1 Gambar [Kembali]

2.2 Video [Kembali]

[Klik di sini]

3. Download [Kembali]

[Klik di sini]

Tidak ada komentar:

Posting Komentar